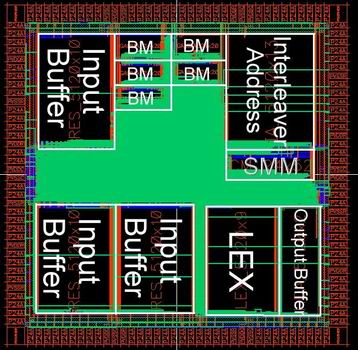

1、A Low Power VLSI

Implementation for Variable Length Decoder in MPEG-1 Layer III

Designer:Wen Cheng-Chen

Operating Voltage : 3V

Clock Frequency : 20MHz

Power dissipation : 1.02mW

Gate Count : 13886

Die Size : 2.5mm * 2.5mm

Manufacture : 0.35 1P4M

2、MP3 Audio Decoder

Designer:Ya Chao-Yang

Operating Voltage : 3V

Clock Frequency : 20MHz

Power dissipation : 28.89mW

Gate Count : 80908

Die Size : 3.5mm * 3.5mm

Manufacture : 0.35 1P4M

3、Watermark for JPEG

Designer : Chung Yi-Lu

Operating Voltage : 3V

Clock Frequency : 40MHz

Power dissipation : 24.026mW

Gate Count : 46374

Die Size : 3.064mm * 3.064mm

Manufacture : 0.35 1P4M

4、MPEG-4 Shape Encoder

Designer : Chia Ping-Chen

Operating Voltage : 2.5V

Clock Frequency : 40MHz

Power dissipation : 127mW

Gate Count : 33821

Die Size : 2.4mm * 2.4mm

Manufacture : TSMC 25 1P5M

5、Watermark Embedding System in MPEG Video

Encoder

Designer : Chih Yen-Wu

Operating Voltage : 3V

Clock Frequency : 50MHz

Power dissipation : 18.7858mW

Gate Count : 29128

Die Size : 3.254mm * 3.254mm

Manufacture : 0.35 1P4M

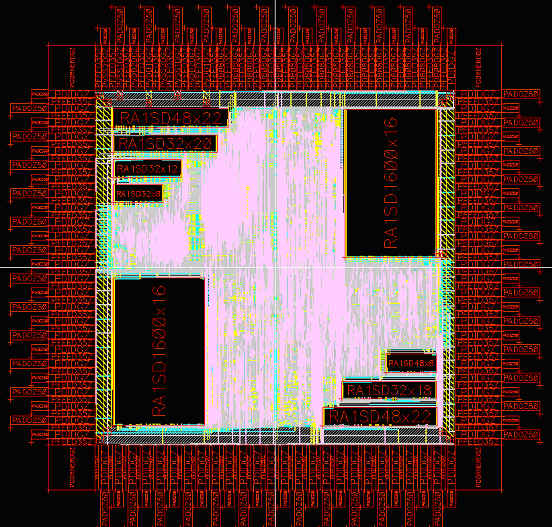

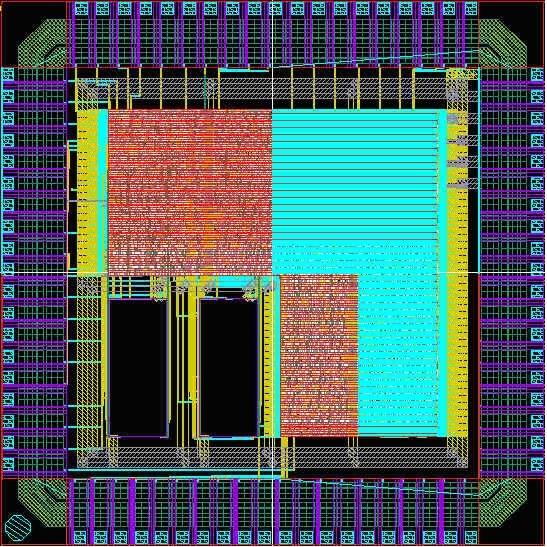

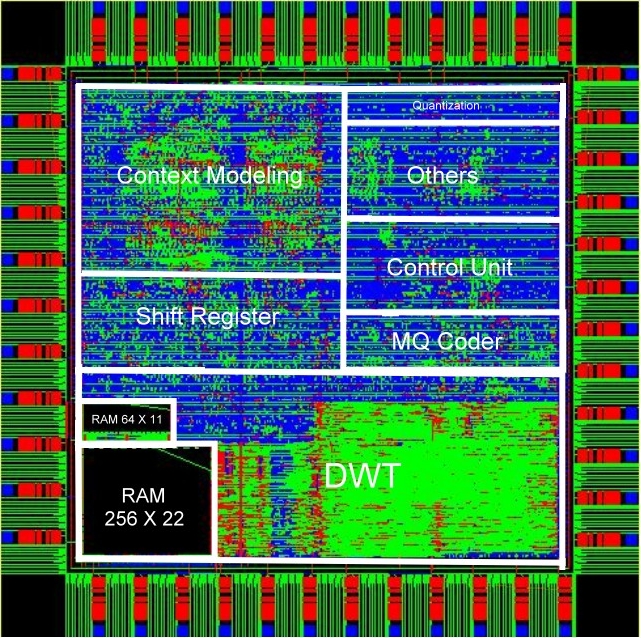

6、JPEG2000 Encoder

Designer : Yu Nan-Pan、Lien Tsung-Tsai

Operating Voltage : 3V

Clock Frequency : 33MHz

Power dissipation : 382.6mW

Gate Count : 87597

Die Size : 2.7mm * 2.7mm

Manufacture : 0.35 1P4M

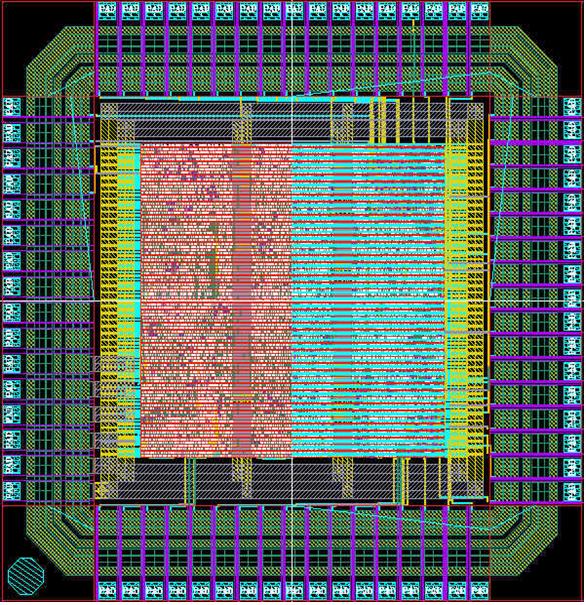

7、MPEG 2/4 AAC Audio Decoder

Designer : Chun Nan-Liu

Operating Voltage : 2.5V

Clock Frequency : 33MHz

Power dissipation : 20.9mW at 3.3MHz

Gate Count : 89909

Die Size : 3.605mm * 3.605mm

Manufacture : 0.25 1P4M

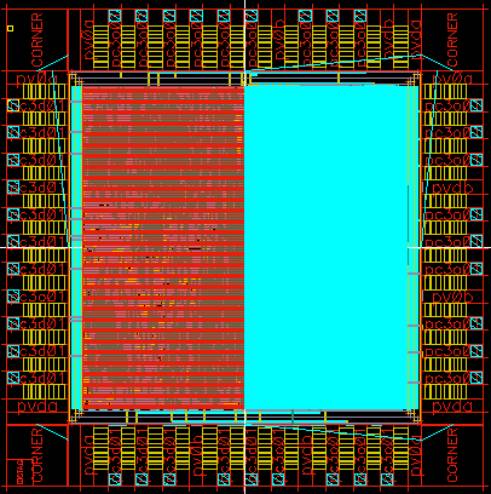

8、Turbo Decoder for 3GPP

Designer : Chen Hung-Lin

Operating Voltage : 1.8V

Clock Frequency : 149MHz

Power dissipation : 20.9mW at 3.3MHz

Gate Count : 116000

Die Size 3.12mm * 3.12mm

Manufacture : 0.25 1P6M