MP3 Single Chip Audio Decoder

Motivation:

MPEG Layer III (MP3) audio coding algorithm is a

widely used audio coding standard

General implementation solution is used by DSP

processor or RISC processor

q Not an

optimal approach

q Increasing

power consumption and area

q Large

memory usage

Until now, no efficient pure-ASIC approach is

used to realize a full functionality MP3 audio decoder

Features:

MP3 domain-knowledge is too complex and not easy

for VLSI implementation

q Variable

length of main data (Bit reservoir)

q No-uniform quantization

q Modified DCT

q Polyphase subband decomposition

q Large Huffman decoding table (34 tables)

q 4 types of window switching (Long, Short,

Long-to-Short, Short-to-Long)

q Stereo signal process

q �K

Key

features and claims:

A total solution Star-IP

q No other IP-based integration is needed

q No domain-knowledge is used in realization

An efficient pure-ASIC approach

q

Largely decrease power

consumption

q Largely decrease memory usage

Summary:

A single chip (without any programming

efforts and hardware), pure - ASIC MP3 decoder can be integrated into many

multimedia applications easily, such as

A MP3 decoder with 13KBytes memory and 3MHz operation frequency is achieved and consumes only 33mW

q A low

power variable length decoder architecture is used for Huffman decoding. The

power consumption can reduce about 67%

q In the

de-quantization, the table size is reduced from 8191 to 256

q CSD

representation is used to reduce power consumption of the hardware

implementation

q

Base on the symmetrical properties of

cosine coefficients, the computation of DWIMDCT can reduce 50% and the

computation of SIMDCT can reduce 25%

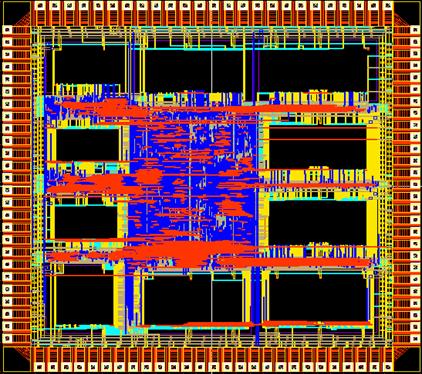

Chip summary:

|

Gate count |

Glue Logic Memory Total |

|

Pre-processing unit Post-processing unit Total |

63522 77146 140669 29970 248984 278954 94283 349811 444094 |

|

Die

size |

|

|

Package |

128

CQFP |

|

Memory |

13k

Bytes |

|

Clock

rate (max) |

20MHz |

|

Clock

rate (real time) |

3MHz |

|

Power (report

by Synopsys Nonasim |

33.6mW |

Made

by ���T��