A Configurable Common Filterbank Processor for Multi-Standard Audio Decoder

Less gate count and one cycle per codeword

No audio standard can replace the other in the near future

Single device has to support multi-standard

Individual hardware for each standard is uneconomical

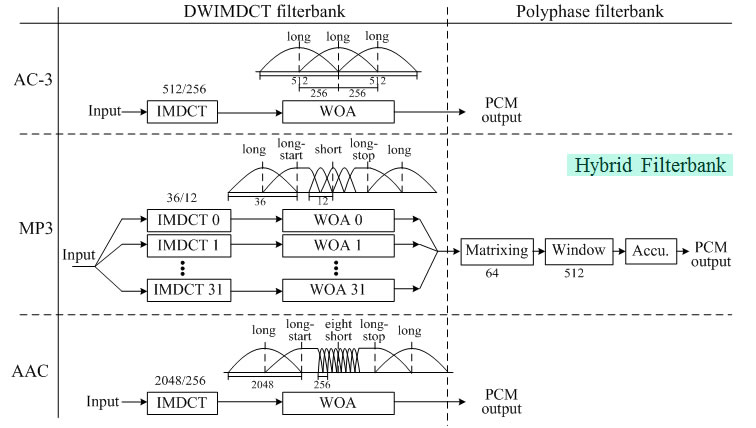

A Configurable Common Filterbank Processor to support AC-3, MP3 and AAC decoding

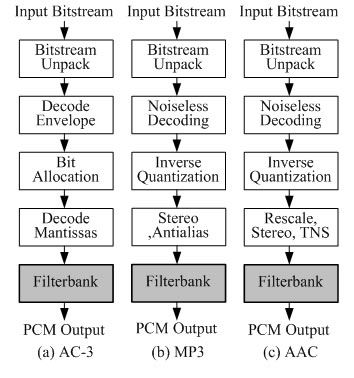

They have similar flows

Very suitable for hardware integration

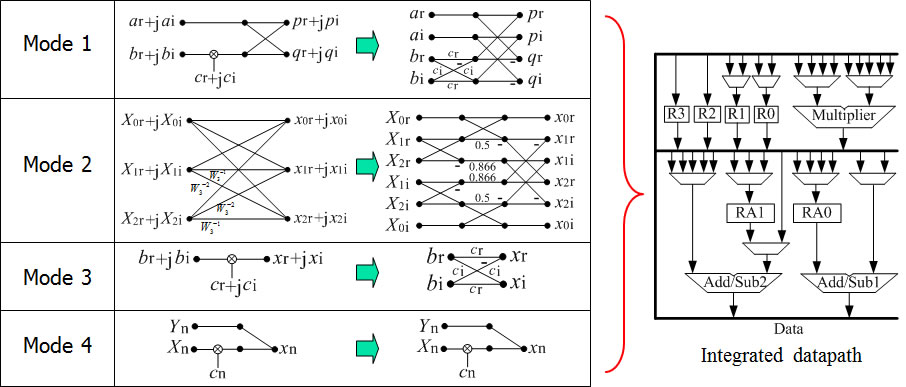

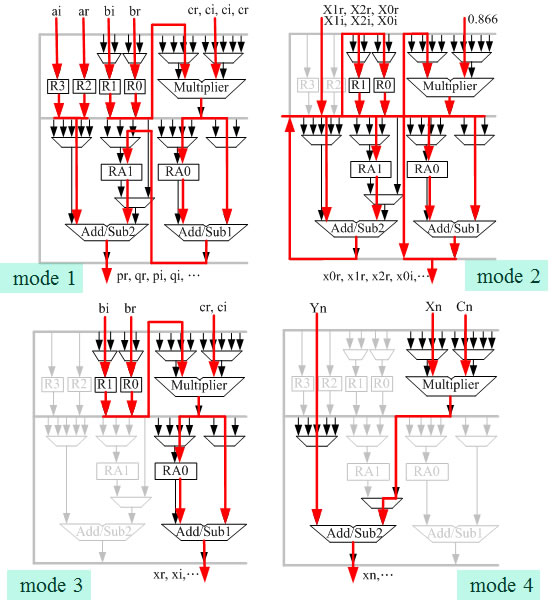

Mode 1: even-point IFFT with radix-2 butterfly unit

Mode 2: odd-point IFFT with radix-3 IFFT unit

Mode 3: pre/post twiddle with complex multiplication

Mode 4: WOA with real multiplication

Configuration of Four Operation Modes

Mode 1: even-point IFFT with radix-2 butterfly unit

Mode 2: odd-point IFFT with radix-3 IFFT unit

Mode 3: pre/post twiddle with complex multiplication

Mode 4: WOA with real multiplication

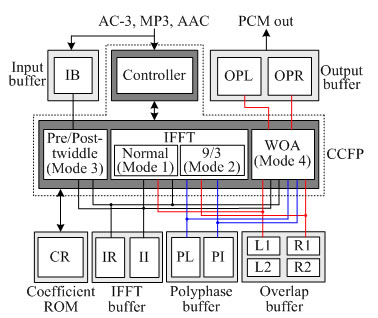

Overall architecture of CCFP

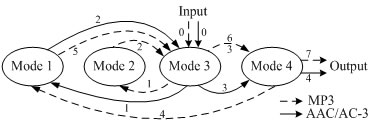

Mode transaction diagram

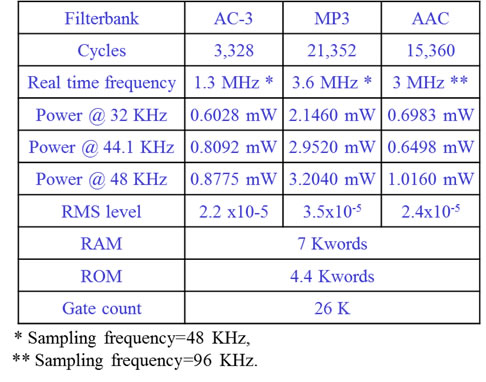

Summaries of CCFP

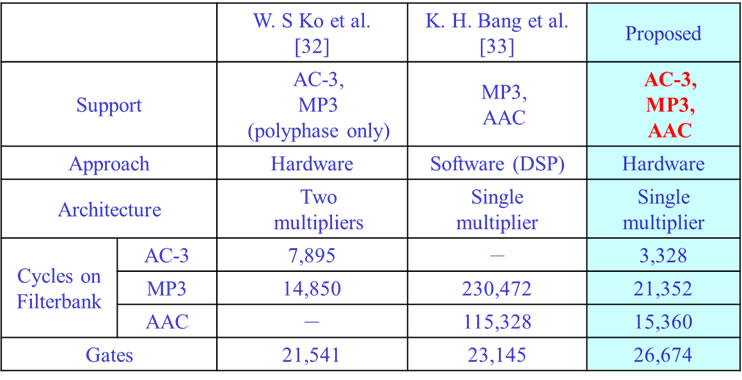

Comparisons with Previous Multi-Standard Designs

Comparing to [33] 10x and 7.5x speed up for MP3 and AAC

Comparing to [32] 2x speed up for AC-3

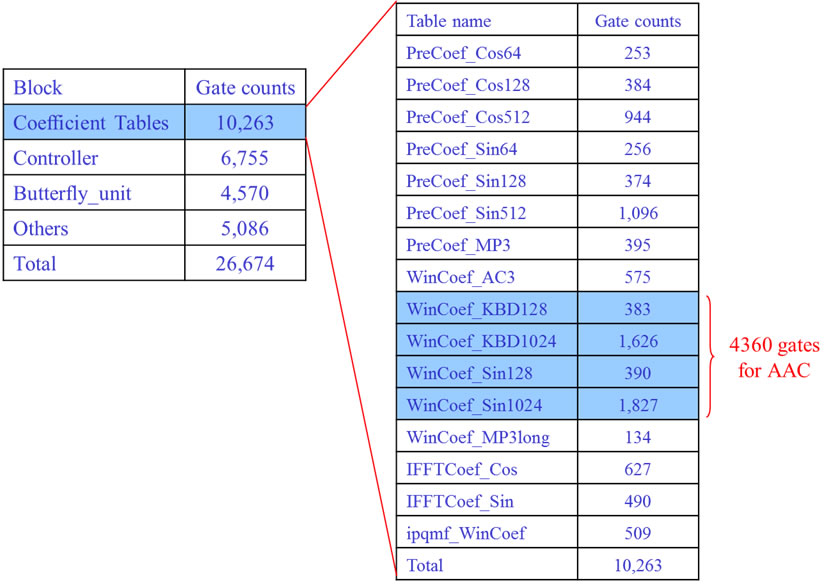

Detailed Gate Counts Analysis of CCFP

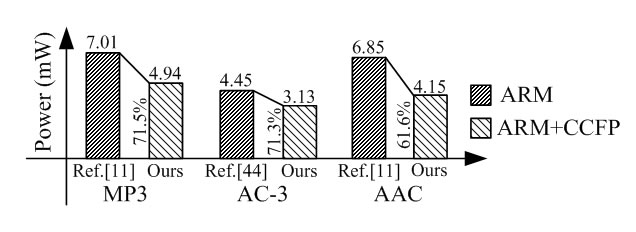

Power Reduction Rate of the Proposed Design

28%~38% power saving for MP3, AC-3 and AAC comparing to pure ARM solutions

MP3: 33.4 MHz (78%)

AC3: 21.2 MHz (80%)

AAC: 32.6 MHz (54%)