以PACDSP平行化組語實現之高效能AAC解碼器

A High Performance AAC Decoder on PACDSP Platform using

Parallelized Assembly Coding Technique

Demo影片

I. 作品簡介

本作品使用一具有5-way VLIW架構的PAC DSP平台上開發高效能的MPEG AAC解碼器系統,在Versatile Platform上除了原本的ARM processor,另外在logic tile加入了PAC DSP,使整個系統成為Dual Core的平台。ARM的部份負責處理使用者的輸入介面、將AAC檔載入到SDRAM,PAC DSP的部份處理整個AAC解碼器運算及運算所需的輸入與輸出資料的傳送接收等,ARM與DSP之間可以透過memory mapped register進行溝通並利用簡單的Finite State Machine來控制解碼的流程。輸出的介面可以透過Versatile上的Audio Codec (AACI) 將解碼後的PCM data直接透過喇叭進行播放,其中將PCM data從SDRAM讀取到AACI FIFO的動作則是透過Versatile上的DMA機制來處理,而不影響到ARM與DSP的處理程序。

AAC解碼器系統架構圖

II. 設計重點

(1)使用組合語言撰寫整個AAC解碼器,並非只是將C Code單純porting到組合語言的過程,由於PAC DSP屬於VLIW架構且具有5-way的平行處理能力,程式撰寫將針對指令的平行度作最佳化。

(2)針對AAC解碼器中複雜度較高的模組(例:Filterbank),搭配適合的快速演算法來降低運算量並加速。

(3)Huffman解碼模組針對variable bit length進行處理,除了增加search的速度外,也減少Huffman table消耗的記憶體資源。

(4)利用PAC DSP提供之特殊指令集,配合各個模組的特性發揮這些指令的效能,降低各模組的計算量,減少所需的工作週期 (cycle count)。

(5)相對於以C Code方式實現的AAC解碼器,我們能以更低的操作頻率和更少的工作週期即時(Real-Time)解碼AAC bitstream,此外其功率消耗也因而大幅減低。

III. AAC解碼流程

IV. 設計方法及創意

Noiseless Decoding

Count leading sign with 2-level table lookup

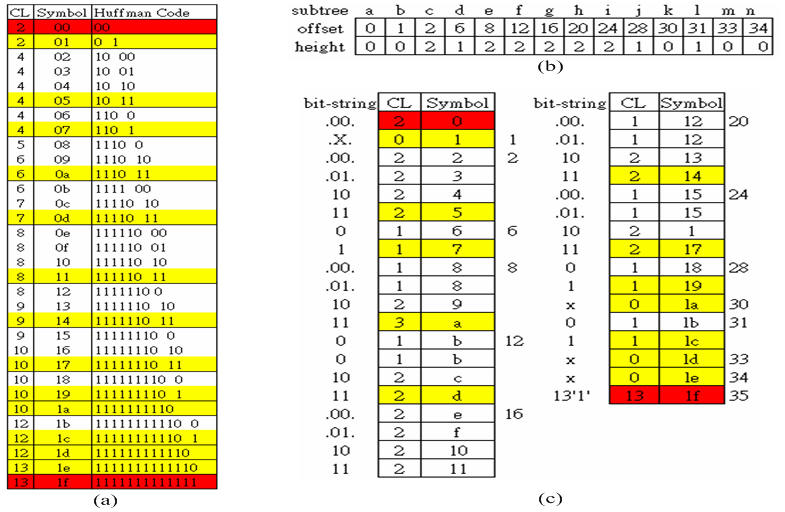

在PAC DSP中有個CLS指令可以計算leading sign bit的位元數,我們分析AAC Huffman table可以充分利用這個指令的特性,如圖(a)所示,將原本的Huffman table根據前面的leading sign bit做分群的動作,再將此分群的資訊建立ㄧ個索引的表如圖(b)所示,最後實際的codeword資訊則是建立在圖(c)中,利用CLS的指令可以很快的進到相對應的Sub-group解出codeword,除了解碼速度很快之外,table size也很小。

Inverse Quantizer

256-size table lookup with interpolation iq = |x_quant|4/3

| Linear Search | Binary Search | Two-step table lookup | Ours (Count leading sign) | |

| HCB_1 | 81 | 162 | 160 | 92 |

| HCB_2 | 81 | 162 | 113 | 104 |

| HCB_3 | 81 | 162 | 793 | 122 |

| HCB_4 | 81 | 162 | 226 | 120 |

| HCB_5 | 81 | 162 | 288 | 112 |

| HCB_6 | 81 | 162 | 166 | 112 |

| HCB_7 | 64 | 128 | 218 | 97 |

| HCB_8 | 64 | 128 | 123 | 97 |

| HCB_9 | 169 | 338 | 603 | 228 |

| HCB_10 | 169 | 338 | 290 | 217 |

| HCB_11 | 289 | 578 | 408 | 345 |

| HCB_SF | 121 | 242 | 2060 | 173 |

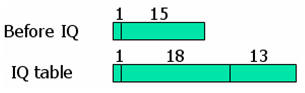

數值小於256直接查表,大於256則用內插。因為PAC DSP只支援16bit x 16bit乘法,而IQ運算需要32bit x 16bit乘法,所以要分兩次做再加起來,再調整為所需的format,如圖所示,D5存rem所以都是整數而AC0前16bit都是0,只取後半部即可。

Scale Factors

4-size table lookup with shift operation gain = 20.25(sf-100)

設計中gain的部份只存20,20.25,20.5,20.75搭配shift完成非線性的運算。如圖左所示,如果rescale的值往左shift 12 bits,整數部分差了3 bit準確度,利用AC暫存器增加8 bit精準度,如圖右所示,rescale的值往左shift 12 bits,再調整為Q23.8 format,誤差只有1 bit。

Middle/Side and Intensity stereo

Flow integration and loop reduction

圖左及圖右分別表示M/S跟intensity的解碼流程圖,原本獨立的兩個流程,經由分析發現M/S只有common_window=1時ms_mask_pre才不為0,所以這兩個流程可以共用相同參數,我們將M/S跟intensity整合成單一流程並省下50%的運算量。

M/S stereo解碼流程 Intensity stereo解碼流程

整合之M/S和Intensity stereo解碼流程圖

Filterbank

N/4-point IFFT fast algorithm for IMDCT

Two cluster parallel optimization

Filterbank占了整個AAC解碼流程裡最高的運算量,而IMDCT是其中最主要的運算且消耗最多的運算複雜度,因此需要使用快速演算法來降低整個運算量。 我們採用以IFFT為核心轉換的快速演算法來實現IMDCT,其運算複雜度可從原本的O(N2)降到O(Nlog2N)。

IFFT快速演算法可大略分為下列四個步驟

(1)Pre-twiddle

(2)N/4-point Complex IFFT

(3)Post-twiddle

(4)De-interleaving

Filterbank快速演算法流程圖

V. ARM與DSP系統整合

本設計中ARM進行解碼流程的控制,將AAC bitstream送至DSP local memory、接收DSP解碼完之PCM data及播放的動作等,而DSP接收到AAC bitstream及啟動訊號(dsp_flag)之後完成AAC的解碼流程並送出PCM data,為了提升ARM與DSP的效率,兩個處理器以平行化在處理,也就是DSP處理目前的frame時,ARM已經在處理下一個frame。 為了減少控制複雜度,每一次從Versatile的SDRAM固定搬4KByte資料到DSP local memory,記錄每個frame結束的位置,下一次從此位置重新搬移4KByte資料。

ARM與DSP系統整合流程圖

VI. 實驗結果

AAC設計規格列表

| Standard | MPEG-2 AAC (13818-7) |

| Profile | LC (low complexity) |

| Bitstream format | ADIF |

| Channel | Mono/Stereo |

| Sampling frequency | 8-96KHz |

| Output | 16-bit PCM |

AAC解碼器Cycle count統計

| Functions | Cycles |

| Huffman | 32,557 |

| IQ、Rescale |

54,886 |

| M/S | 3,621 |

| TNS | 94,208 |

| Filterbank | 165,008 |

| Total | 350,280 |

AAC解碼器使用資源需求表

| Operation frequency | 15 MHz (Fs=44.1KHz) |

| RMS level | 6.4 x 10-5 (Limited accuracy) |

| Program memory | 27KB |

| Data ROM | 14.33KB |

| Data RAM | 12.66KB |

VII. 結論

(1)本設計以PAC DSP組合語言開發一最佳化MPEG-2 AAC解碼器,每個模組都經過最佳化處理,不論是演算法或解碼流程的簡化,甚至以高平行度化的撰寫語法來最佳化等。

(2)本系統只需以15MHz操作頻率即可達即時播放之性能,local memory與code size都只需27KB。

(3)利用Versatile上的雙核心平台完整驗證AAC解碼器,透過我們設計的使用者介面,使用者可直接選擇想要播放之歌曲,立即從喇叭聆聽由AAC解碼器所解碼之音樂歌曲。