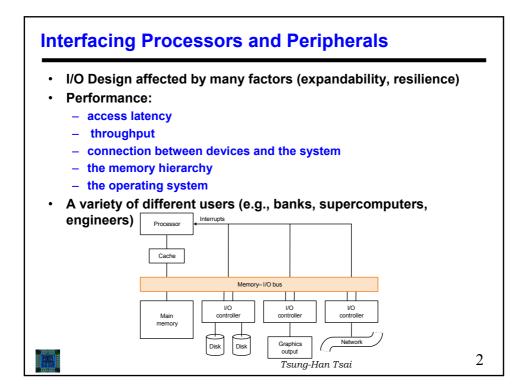

## **I/O**

## Important but neglected

"The difficulties in assessing and designing I/O systems have often relegated I/O to second class status"

- Performance measures for I/O systems: see pp.639

- Very diverse devices (Section 8.3)

| Device           | Behavior        | Partner | Data rate (KB/sec) |

|------------------|-----------------|---------|--------------------|

| Keyboard         | input           | human   | 0.01               |

| Mouse            | input           | human   | 0.02               |

| Voice input      | input           | human   | 0.02               |

| Scanner          | input           | human   | 400.00             |

| Voice output     | output          | human   | 0.60               |

| Line printer     | output          | human   | 1.00               |

| Laser printer    | output          | human   | 200.00             |

| Graphics display | output          | human   | 60,000.00          |

| Modem            | input or output | machine | 2.00-8.00          |

| Network/LAN      | input or output | machine | 500.00-6000.00     |

| Floppy disk      | storage         | machine | 100.00             |

| Optical disk     | storage         | machine | 1000.00            |

| Magnetic tape    | storage         | machine | 2000.00            |

| Magnetic disk    | storage         | machine | 2000.00-10,000.00  |

| Bus               | MBus    | Summit  | Challenge | XDBus        |

|-------------------|---------|---------|-----------|--------------|

| Originator        | Sun     | HP      | SGI       | Sun          |

| Clock Rate (MHz)  | 40      | 60      | 48        | 66           |

| Address lines     | 36      | 48      | 40        | muxed        |

| Data lines        | 64      | 128     | 256       | 144 (parity) |

| Data Sizes (bits) | 256     | 512     | 1024      | 512          |

| Clocks/transfer   |         | 4       | 5         | 4?           |

| Peak (MB/s)       | 320(80) | 960     | 1200      | 1056         |

| Master            | Multi   | Multi   | Multi     | Multi        |

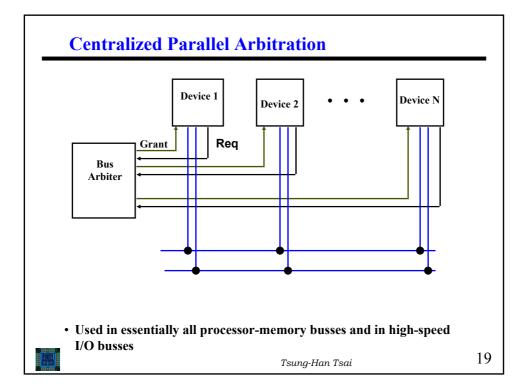

| Arbitration       | Central | Central | Central   | Central      |

| Slots             |         | 16      | 9         | 10           |

| Busses/system     | 1       | 1       | 1         | 2            |

13 inches

Length

12? inches

17 inches

20

| Bus                | SBus          | TurboChannel | MicroChannel  | PCI           |

|--------------------|---------------|--------------|---------------|---------------|

| Originator         | Sun           | DEC          | IBM           | Intel         |

| Clock Rate (MHz)   | 16-25         | 12.5-25      | async         | 33            |

| Addressing         | Virtual       | Physical     | Physical      | Physical      |

| Data Sizes (bits)  | 8,16,32       | 8,16,24,32   | 8,16,24,32,64 | 8,16,24,32,64 |

| Master             | Multi         | Single       | Multi         | Multi         |

| Arbitration        | Central       | Central      | Central       | Central       |

| 32 bit read (MB/s) | 33            | 25           | 20            | 33            |

| Peak (MB/s)        | 89            | 84           | 75            | 111 (222)     |

| Max Power (W)      | 16            | 26           | 13            | 25            |

| • High speed I/C   | ) bus         |              |               |               |

| - Examples:        | graphics, fa  | st networks  |               |               |

| – Limited nu       | mber of dev   | vices        |               |               |

| – Data trans       | fer bursts at | full rate    |               |               |

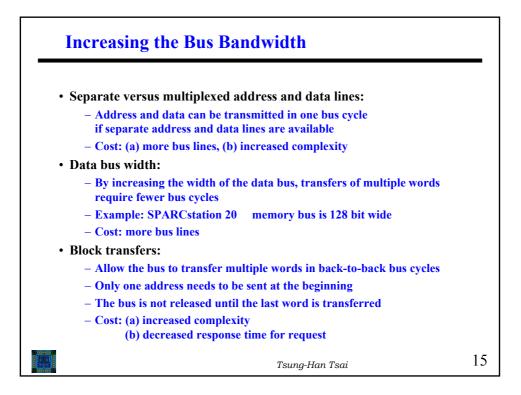

## Summary of Bus Options

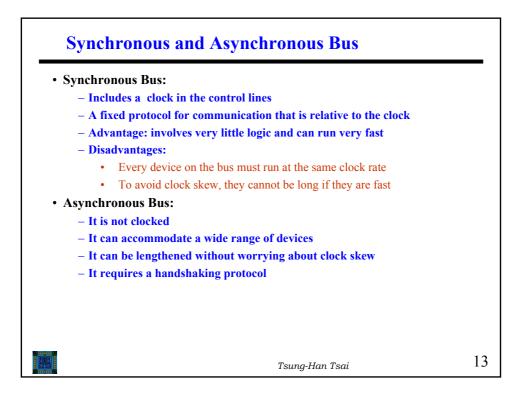

| •Option                                     | High performance                        | Low cost                              |

|---------------------------------------------|-----------------------------------------|---------------------------------------|

| •Bus width                                  | Separate address<br>& data lines        | Multiplex address<br>& data lines     |

| •Data width                                 | Wider is faster<br>(e.g., 32 bits)      | Narrower is cheaper<br>(e.g., 8 bits) |

| •Transfer size                              | Multiple words has<br>less bus overhead | Single-word transfer<br>is simpler    |

| •Bus masters                                | Multiple<br>(requires arbitration)      | Single master<br>(no arbitration)     |

| <ul><li>Clocking</li><li>Protocol</li></ul> | Synchronous<br>pipelined                | Asynchronous<br>Serial                |