| Summary:                                                      |                                                                                           |                                                                |                                |                                     |  |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------|-------------------------------------|--|

| -                                                             |                                                                                           |                                                                |                                |                                     |  |

|                                                               |                                                                                           |                                                                |                                |                                     |  |

|                                                               |                                                                                           |                                                                |                                |                                     |  |

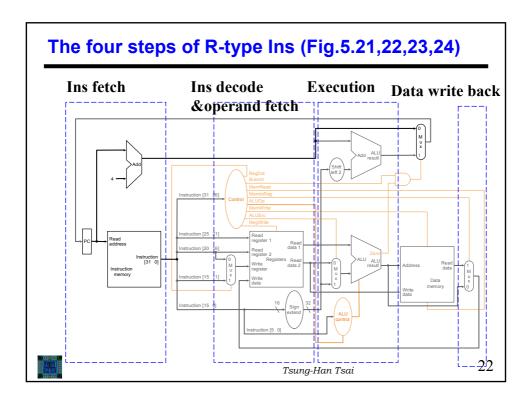

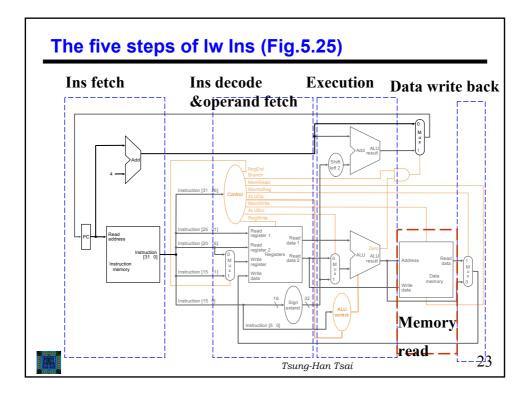

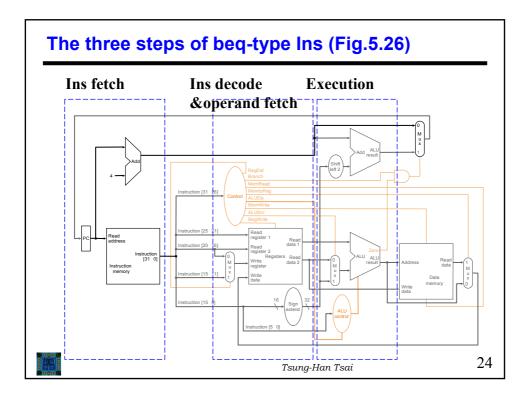

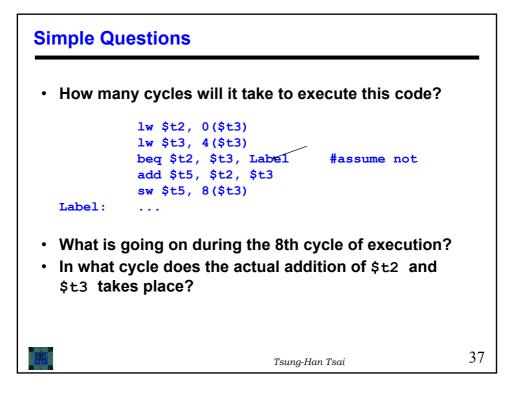

| Step name                                                     | Action for R-type instructions                                                            | Action for memory-reference                                    | Action for branches            | Action for                          |  |

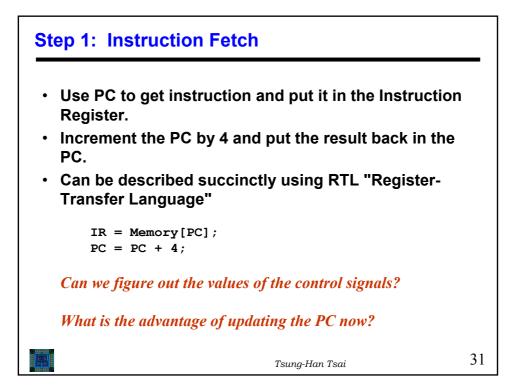

| Instruction fetch                                             | IR = Memory[PC]<br>PC = PC + 4                                                            |                                                                |                                |                                     |  |

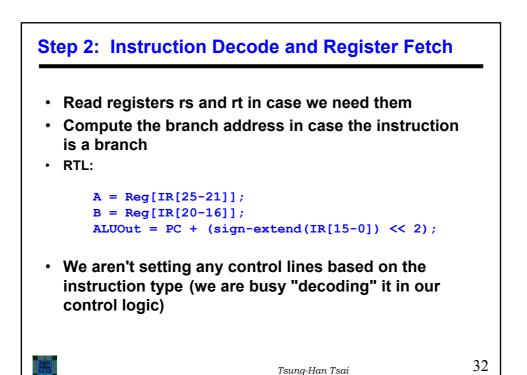

| Instruction<br>decode/register fetch                          | A = Reg [IR[25-21]]<br>B = Reg [IR[20-16]]<br>ALUOut = PC + (sign-extend (IR[15-0]) << 2) |                                                                |                                |                                     |  |

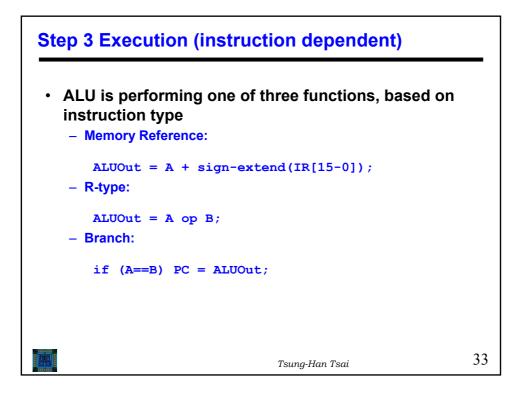

| Execution, address<br>computation, branch/<br>jump completion | ALUOut = A op B                                                                           | ALUOut = A + sign-extend<br>(IR[15-0])                         | if (A ==B) then<br>PC = ALUOut | PC = PC [31-28] II<br>(IR[25-0]<<2) |  |

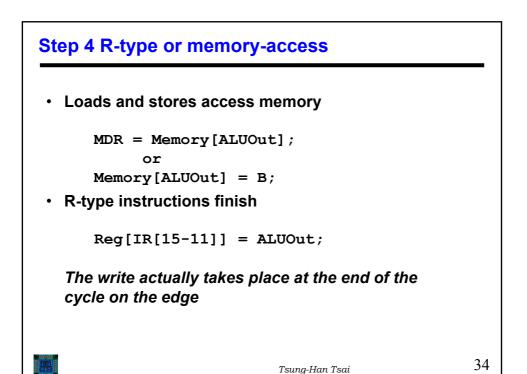

| Memory access or R-type<br>completion                         | Reg [IR[15-11]] =<br>ALUOut                                                               | Load: MDR = Memory[ALUOut]<br>or<br>Store: Memory [ALUOut] = B |                                |                                     |  |

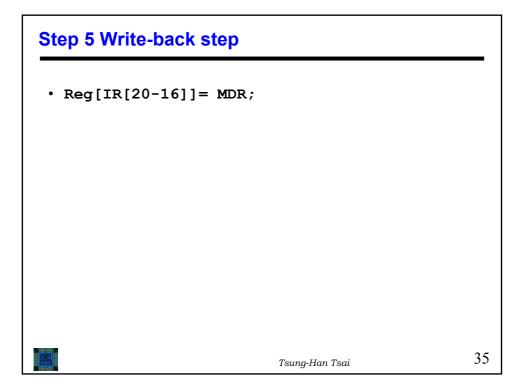

| Memory read completion                                        |                                                                                           | Load: Reg[IR[20-16]] = MDR                                     |                                |                                     |  |

36

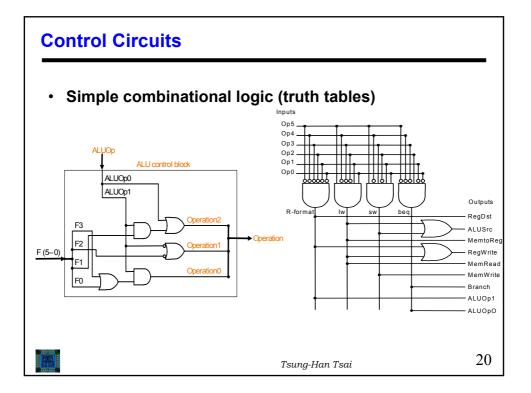

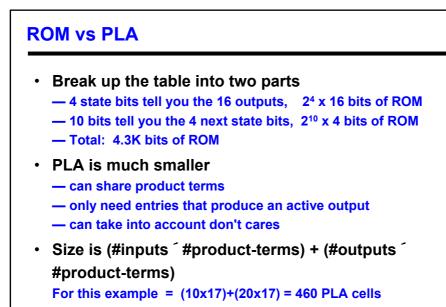

PLA cells usually about the size of a ROM cell

(slightly bigger)

Tsung-Han Tsai

45

| Field name       | Value        | Signals active                | Comment                                                                                                                         |  |

|------------------|--------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

|                  | Add          | ALUOp = 00                    | Cause the ALU to add.                                                                                                           |  |

| ALU control      | Subt         | ALUOp = 01                    | Cause the ALU to subtract; this implements the compare for<br>branches.                                                         |  |

|                  | Func code    | ALUOp = 10                    | Use the instruction's function code to determine ALU control.                                                                   |  |

| SRC1             | PC           | ALUSrcA = 0                   | Use the PC as the first ALU input.                                                                                              |  |

|                  | A            | ALUSrcA = 1                   | Register A is the first ALU input.                                                                                              |  |

| SRC2             | В            | ALUSrcB = 00                  | Register B is the second ALU input.                                                                                             |  |

|                  | 4            | ALUSrcB = 01                  | Use 4 as the second ALU input.                                                                                                  |  |

|                  | Extend       | ALUSrcB = 10                  | Use output of the sign extension unit as the second ALU input.                                                                  |  |

|                  | Extshft      | ALUSrcB = 11                  | Use the output of the shift-by-two unit as the second ALU input.                                                                |  |

| Register         | Read         |                               | Read two registers using the rs and rt fields of the IR as the register<br>numbers and putting the data into registers A and B. |  |

|                  | Write ALU    | RegWrite,                     | Write a register using the rd field of the IR as the register number and                                                        |  |

|                  |              | RegDst = 1,<br>MemtoReg = 0   | the contents of the ALUOut as the data.                                                                                         |  |

|                  | Write MDR    | RegWrite,                     | Write a register using the rt field of the IR as the register number and                                                        |  |

|                  |              | RegDst = 0,<br>MemtoReg = 1   | the contents of the MDR as the data.                                                                                            |  |

| Memory           | Read PC      | MemRead,<br>lorD = 0          | Read memory using the PC as address; write result into IR (and the MDR).                                                        |  |

|                  | Read ALU     | MemRead,<br>lorD = 1          | Read memory using the ALUOut as address; write result into MDR.                                                                 |  |

|                  | Write ALU    | MemWrite,<br>lorD = 1         | Write memory using the ALUOut as address, contents of B as the<br>data.                                                         |  |

| PC write control | ALU          | PCSource = 00<br>PCWrite      | Write the output of the ALU into the PC.                                                                                        |  |

|                  | ALUOut-cond  | PCSource = 01,<br>PCWriteCond | If the Zero output of the ALU is active, write the PC with the contents<br>of the register ALUOut.                              |  |

|                  | jump address | PCSource = 10,<br>PCWrite     | Write the PC with the jump address from the instruction.                                                                        |  |

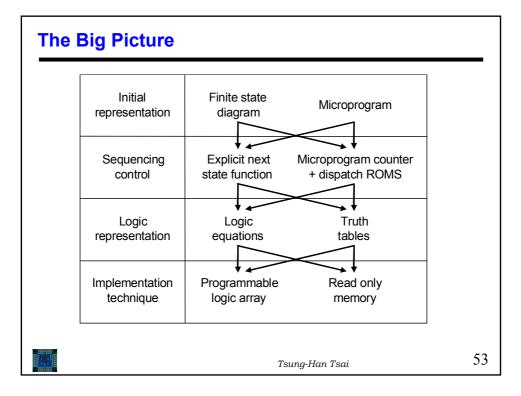

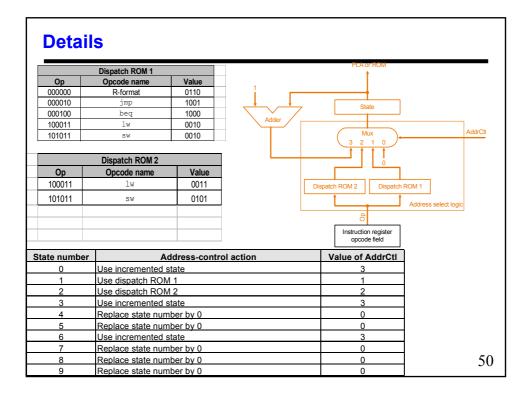

| Sequencing       | Seq          | AddrCtl = 11                  | Choose the next microinstruction sequentially.                                                                                  |  |

|                  | Fetch        | AddrCtl = 00                  | Go to the first microinstruction to begin a new instruction.                                                                    |  |

|                  | Dispatch 1   | AddrCtl = 01                  | Dispatch using the ROM 1.                                                                                                       |  |

|                  | Dispatch 2   | AddrCtl = 10                  | Dispatch using the ROM 2.                                                                                                       |  |

Tsung-Han Tsai