| • L | oop         | with variab | ole array    | index        |                     |             |       |   |

|-----|-------------|-------------|--------------|--------------|---------------------|-------------|-------|---|

| -   | – <u>Ex</u> | ample, p.1  | 26 Lo        | op: g=g      | +A[I];              |             |       |   |

|     |             |             |              | i=i+         |                     |             |       |   |

|     |             |             |              |              | != h) go t          |             |       |   |

|     |             |             | Lo           |              | <u>\$t1,\$s3,\$</u> |             |       |   |

|     |             |             |              |              | <u>\$t1, \$t1,</u>  |             |       |   |

|     |             |             |              |              | \$t1,\$t1,\$        | s5          |       |   |

|     |             |             |              |              | t0,0(\$t1)          |             |       |   |

|     |             |             |              |              | <u>\$s1,\$s1,</u>   |             |       |   |

|     |             |             |              |              | \$s3,\$s3,          |             |       |   |

|     |             |             |              |              | \$s3,\$s2,I         |             |       |   |

|     |             | Note:g,h,l, | j ->\$s1,\$s | s2,\$s3,\$s4 | ;base of            | A is in \$s | 5     |   |

| • W | Vhile       | Loop: see   | p.127        |              |                     |             |       |   |

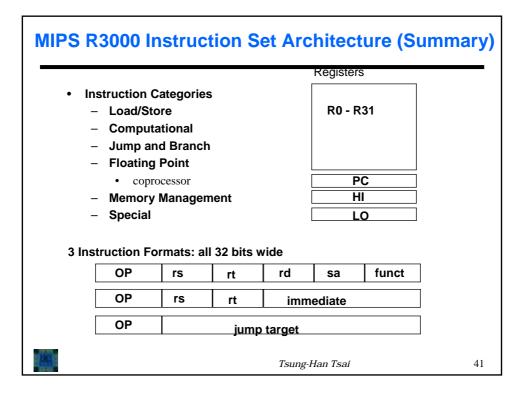

| -   | – Fo        | ormats:     |              |              |                     |             |       |   |

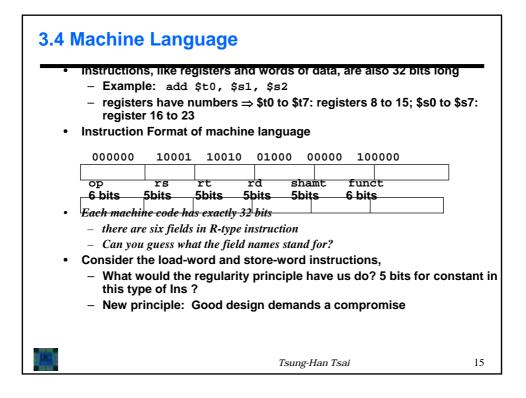

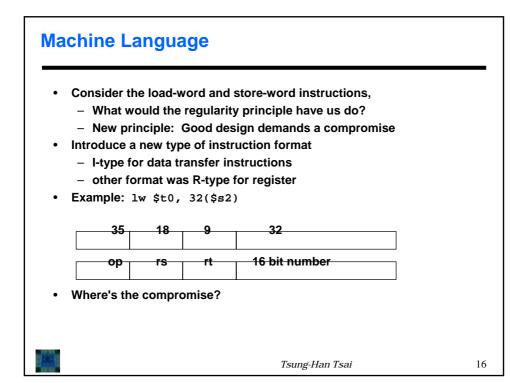

|     | R           | op          | rs           | rt           | rd                  | shamt       | funct |   |

|     | I           | op          | rs           | rt           | 16 b                | it addro    | ess   |   |

|     | J           | ор          |              | 26 b         | it addre            | 255         |       | ] |

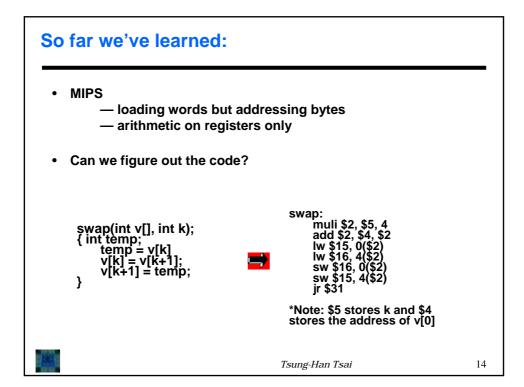

## So far: $\cdot$ <u>mernem</u><u>Dening</u> $\stackrel{\text{df}}{_{1}}$ $\stackrel{\text{ff}}{_{2}}$ $\stackrel{\text{df}}{_{2}}$ $\stackrel{\text{ff}}{_{2}}$ $\stackrel{\text{ff}}{$

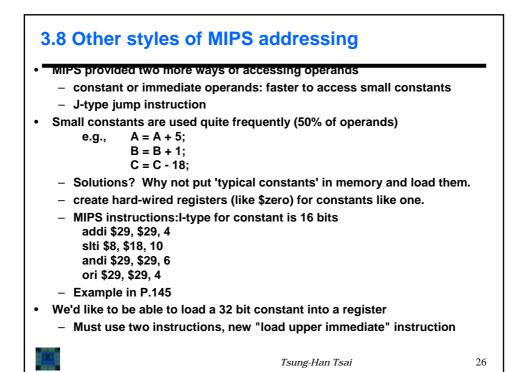

| How about larger o                                                                          | constants?                    |    |

|---------------------------------------------------------------------------------------------|-------------------------------|----|

| • lui \$t0, 101010                                                                          | 01010101010 filled with zeros |    |

| • Then must get the lower<br>ori \$t0, \$t0, 10                                             |                               |    |

|                                                                                             | 01010 0000000000000           |    |

| ori<br>1010101010101                                                                        | 1010 101010101010             |    |

| U U                                                                                         | and jumps: example in p.149   |    |

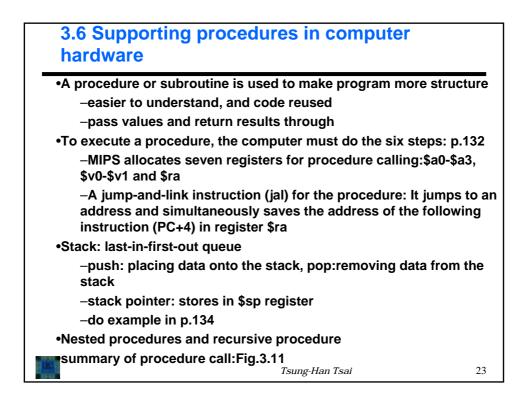

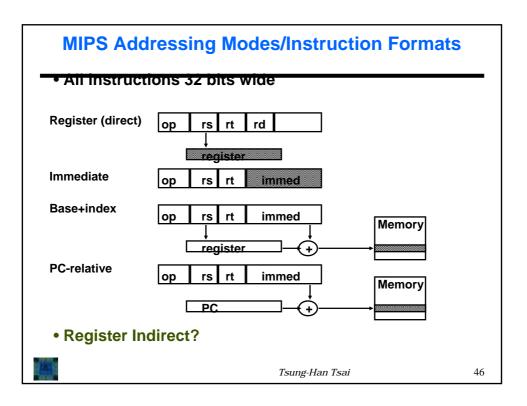

| <ul> <li>MIPS addressing mode s         <ul> <li>Register addressing</li> </ul> </li> </ul> | -                             |    |

| <ul> <li>Base or displacement</li> </ul>                                                    | nt addressing                 |    |

| <ul> <li>Immediate addressin</li> <li>BC relative addressin</li> </ul>                      | 5                             |    |

| <ul> <li>PC-relative addressin</li> <li>Pseudodirect addres</li> </ul>                      | 0                             | 28 |

## Five MIPS addressing modes

| ор             | rs        | rt                         | Im m ediate |   |                 |                  |

|----------------|-----------|----------------------------|-------------|---|-----------------|------------------|

|                |           |                            |             |   |                 |                  |

|                | ter addr  |                            |             |   |                 |                  |

| оp             | rs        | rt                         | rd funct    |   | Regis           |                  |

|                |           |                            |             |   | → Regi          | ster             |

| 2 B            | address   | in a                       |             |   |                 |                  |

| ор             | rs        | rt                         | Address     |   | Mem             | огу              |

|                |           |                            |             |   |                 |                  |

|                |           |                            |             |   |                 |                  |

|                |           | Reg                        | ister       |   | Byte Halfword   | Word             |

|                |           | Reg                        | ister       | ÷ | + Byte Halfword | Word             |

| 4. PC-re<br>op | lative ad |                            |             | + | • Byte Halfword |                  |

| -              | -         | ldressin<br>rt             | Address     |   | M em            | ory              |

| -              | -         | ldressin<br>rt             |             |   |                 | ory              |

| -              | -         | ldressin<br>rt             | Address     |   | M em            | ory              |

| -              | -         | ldressin<br>rt             | Address     |   | M em            | ory              |

| 0 p            | rs        | Idressin<br>rt             | Address     |   | M em            | ory              |

| op<br>5. Pseuc | -         | Idressin<br>rt             | Address     |   | M em            | ory<br>rd        |

| 0 p            | rs        | Idressin<br>rt             | Address     |   |                 | ory<br>rd        |

| op<br>5. Pseuc | rs        | Idressin;<br>rt<br>address | Address     |   |                 | ory<br>rd<br>ory |

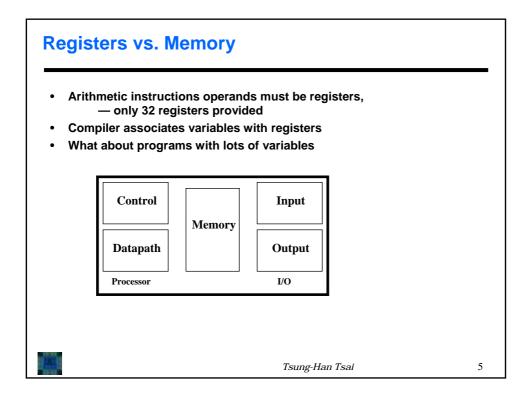

|                                 |                                                                    |                        | MIPS or                                                                                                                                                                                                                                                                            | erands                                      |                                   |  |

|---------------------------------|--------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------|--|

| Name                            | Example                                                            | 2                      | Comments                                                                                                                                                                                                                                                                           |                                             |                                   |  |

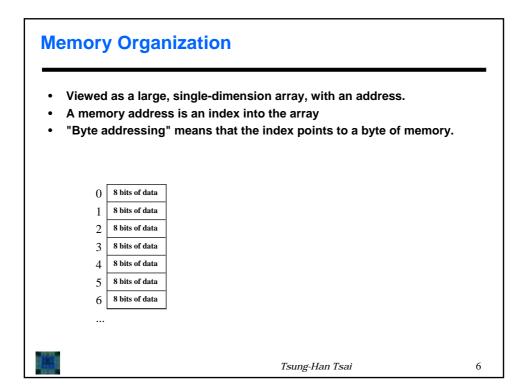

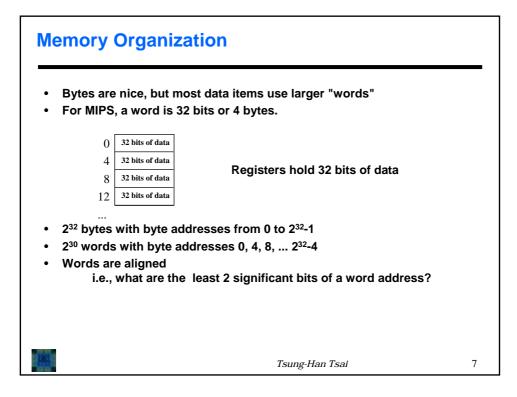

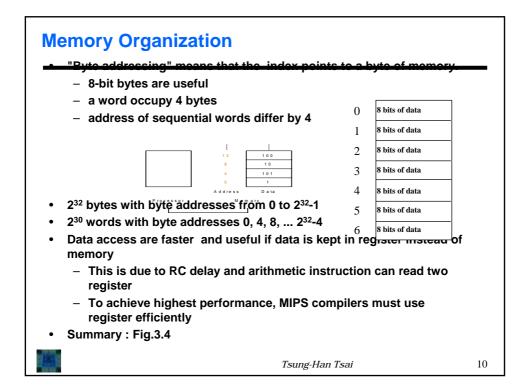

| 32 registers                    | \$s0-\$s7, \$t0-\$t<br>\$a0-\$a3, \$v0-\$v<br>\$fp, \$sp, \$ra, \$ | 9, \$zero,<br>L, \$gp, | Fast locations for data. In MIPS, data must be in registers to perform<br>arithmetic. MIPS register \$zero always equals 0. Register \$at is<br>reserved for the assembler to handle large constants.                                                                              |                                             |                                   |  |

| 2 <sup>30</sup> memory<br>words | Memory[0],<br>Memory[4],,<br>Memory[4294967292]                    |                        | Accessed on the assembler to handle large constants.<br>Accessed only by data transfer instructions. MIPS uses byte addresses, so<br>sequential words differ by 4. Memory holds data structures, such as arrays,<br>and spilled registers, such as those saved on procedure calls. |                                             |                                   |  |

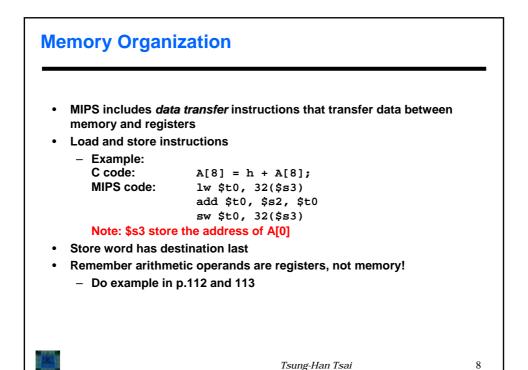

|                                 |                                                                    |                        | MIPS assemb                                                                                                                                                                                                                                                                        | oly language                                |                                   |  |

| Category                        | Instruction                                                        |                        | ample                                                                                                                                                                                                                                                                              | Meaning                                     | Comments                          |  |

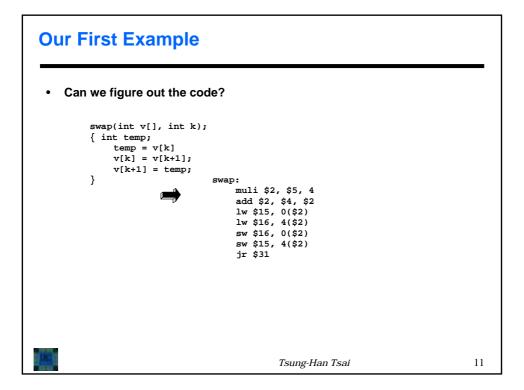

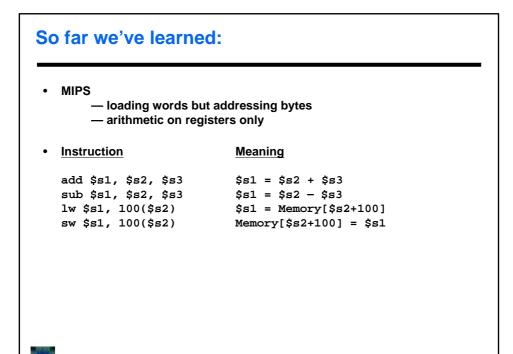

| Arithmetic                      | add                                                                | add \$s1,<br>sub \$s1, |                                                                                                                                                                                                                                                                                    | \$s1 = \$s2 + \$s3<br>\$s1 = \$s2 - \$s3    | Three operands; data in registers |  |

|                                 | subtract                                                           |                        |                                                                                                                                                                                                                                                                                    |                                             | Three operands; data in registers |  |

|                                 | add immediate                                                      | addi \$s1,             |                                                                                                                                                                                                                                                                                    | \$s1 = \$s2 + 100                           | Used to add constants             |  |

|                                 | load word                                                          |                        | 100(\$s2)                                                                                                                                                                                                                                                                          | \$s1 = Memory[\$s2 + 100]                   |                                   |  |

|                                 | store word                                                         |                        | 100(\$s2)                                                                                                                                                                                                                                                                          | Memory[\$\$2 + 100] = \$s1                  | Word from register to memory      |  |

| Data transfer                   | load byte                                                          | lb \$s1,               |                                                                                                                                                                                                                                                                                    | \$s1 = Memory[\$s2 + 100]                   |                                   |  |

|                                 | store byte                                                         |                        | 100(\$s2)                                                                                                                                                                                                                                                                          | Memory[\$s2 + 100] = \$s1                   | Byte from register to memory      |  |

|                                 | load upper immediate                                               | lui \$sl,              | 100                                                                                                                                                                                                                                                                                | \$s1 = 100 * 2 <sup>16</sup>                | Loads constant in upper 16 bits   |  |

| Conditional                     | branch on equal                                                    | beq \$s1,              | \$s2, 25                                                                                                                                                                                                                                                                           | if (\$s1 == \$s2) go to<br>PC + 4 + 100     | Equal test; PC-relative branch    |  |

|                                 | branch on not equal                                                | bne \$s1,              | \$s2, 25                                                                                                                                                                                                                                                                           | if (\$s1 != \$s2) go to<br>PC + 4 + 100     | Not equal test; PC-relative       |  |

| branch                          | set on less than                                                   | slt \$sl,              | \$s2, \$s3                                                                                                                                                                                                                                                                         | if (\$s2 < \$s3) \$s1 = 1;<br>else \$s1 = 0 | Compare less than; for beq, bne   |  |

|                                 | set less than<br>immediate                                         | slti \$sl              | , \$s2, 100                                                                                                                                                                                                                                                                        | if (\$s2 < 100) \$s1 = 1;<br>else \$s1 = 0  | Compare less than constant        |  |

|                                 | jump                                                               | j 2500                 |                                                                                                                                                                                                                                                                                    | go to 10000                                 | Jump to target address            |  |

| Uncondi-                        | jump register                                                      | jr \$ra                |                                                                                                                                                                                                                                                                                    | go to \$ra                                  | For switch, procedure return      |  |

| ional iump                      | iump and link                                                      | jal 2500               |                                                                                                                                                                                                                                                                                    | \$ra = PC + 4; go to 10000                  | For procedure call                |  |

| a.JE EIP + | - displacem | ent          |                |    |

|------------|-------------|--------------|----------------|----|

| 4          | 4           | 8            |                |    |

| JE         | Condition   | Displacement |                |    |

| b.CALL     |             |              |                |    |

| 8          |             |              | 32             |    |

| CA         | LL          |              | Offset         |    |

| 5<br>PUSH  | 3<br>Reg    |              |                |    |

| e.ADD EA   |             |              |                |    |

| 4          | 3 1         |              | 32             |    |

| A D D      | Reg w       |              | Im m ediate    |    |

| f. TEST EI |             |              |                |    |

| 7          |             | 8            | 32             |    |

| TES        | ST w        | Postbyte     | Im m e d ia te |    |

|            |             |              |                |    |

|            |             |              |                |    |

| 1          |             |              | Tsung-Han Tsai | 3' |

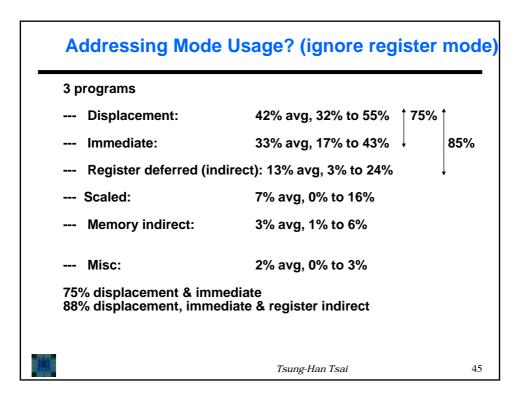

| Addressing mode    | Example        | Meaning                                            |

|--------------------|----------------|----------------------------------------------------|

| Register           | Add R4,R3      | R4← R4+R3                                          |

| Immediate          | Add R4,#3      | R4 ← R4+3                                          |

| Displacement       | Add R4,100(R1) | R4 ← R4+Mem[100+R1]                                |

| Register indirect  | Add R4,(R1)    | $R4 \leftarrow R4+Mem[R1]$                         |

| Indexed / Base     | Add R3,(R1+R2) | $R3 \leftarrow R3+Mem[R1+R2]$                      |

| Direct or absolute | Add R1,(1001)  | R1 ← R1+Mem[1001]                                  |

| Memory indirect    | Add R1,@(R3)   | $R1 \leftarrow R1+Mem[Mem[R3]]$                    |

| Auto-increment     | Add R1,(R2)+   | $R1 \leftarrow R1 + Mem[R2]; R2 \leftarrow R2 + d$ |

| Auto-decrement     | Add R1,?R2)    | $R2 \leftarrow R2$ ; $R1 \leftarrow R1+Mem[R2]$    |

| Typical Operations (I    | ittle change since 1960)                                                                                                                                                        |    |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Data Movement            | Load (from memory)<br>Store (to memory)<br>memory-to-memory move<br>register-to-register move<br>input (from I/O device)<br>output (to I/O device)<br>push, pop (to/from stack) |    |

| Arithmetic               | integer (binary + decimal) or FP<br>Add, Subtract, Multiply, Divide                                                                                                             |    |

| Shift                    | shift left/right, rotate left/right                                                                                                                                             |    |

| Logical                  | not, and, or, set, clear                                                                                                                                                        |    |

| Control (Jump/Branch)    | unconditional, conditional                                                                                                                                                      |    |

| Subroutine Linkage       | call, return                                                                                                                                                                    |    |

| Interrupt                | trap, return                                                                                                                                                                    |    |

| Synchronization          | test & set (atomic r-m-w)                                                                                                                                                       |    |

| String<br>Graphics (MMX) | search, translate<br>parallel subword ops (4 16bit add)                                                                                                                         |    |

|                          | Tsung-Han Tsai                                                                                                                                                                  | 47 |

| ° Rank  | instruction Inte          | eger Average Percent total executed |  |

|---------|---------------------------|-------------------------------------|--|

| 1       | load                      | 22%                                 |  |

| 2       | conditional branch        | 20%                                 |  |

| 3       | compare                   | 16%                                 |  |

| 4       | store                     | 12%                                 |  |

| 5       | add                       | 8%                                  |  |

| 6       | and                       | 6%                                  |  |

| 7       | sub                       | 5%                                  |  |

| 8       | move register-regist      | er 4%                               |  |

| 9       | call                      | 1%                                  |  |

| 10      | return                    | 1%                                  |  |

|         | Total                     | 96%                                 |  |

| ° Simpl | e instructions domination | ate instruction frequency           |  |