Design and Realization of Embedded Compression Algorithm and VLSI Architecture for LCD Display System

ABSTRACT:

The

embedded compression (EC) technique is applied to reduce the memory bandwidth

and capacity in a display system. In this paper, the high-speed EC algorithm is

proposed for advanced-HD specification. It mainly comprises three features: 1) the

associated geometric-based probability model is developed to construct

context-modeling mechanism without context-table; 2) develop content-adaptive Golomb-Rice code and geometric-based binary code as the

entropy coding with minor order of context; and 3) provide the rate control

mechanism to guarantee the saving ratio of memory bandwidth and capacity. With

competitive coding efficiency, the computation-efficiency of the proposed EC algorithm

is about 44% and 40% of FELICS and JPEG-LS. The proposed very-large-scale

integration architecture of entire codec is implemented in TSMC 0.18-μm 1P6M

CMOS technology. Based on pixel-based parallelism and segment-based parallelism

techniques, the encoding/decoding capability reaches Quad Full high definition

(QFHD) (3840 × 2160) at 30 Hz. The maximum throughput is as high as 6.4 Gbit/s. Furthermore, with multilevel parallelism, the

performance can be extended to QHD (2560 × 1440) at 120 Hz and QFHD at 120 Hz

for the double frame rate technique.

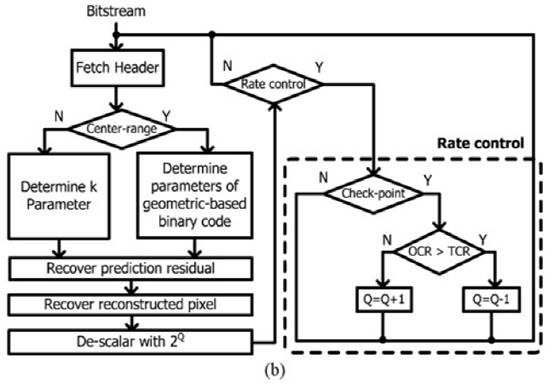

Flow chart:

Encode:

Decode:

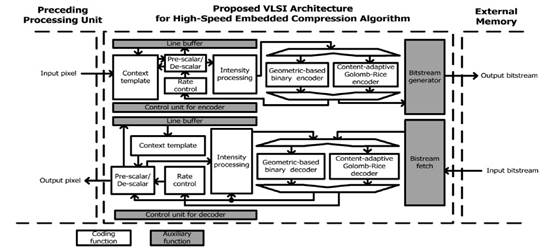

THE proposed VLSI architecture of entire

EC:

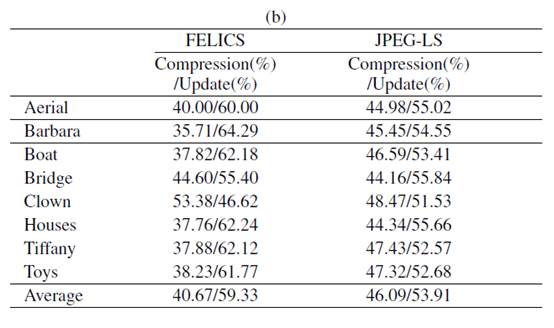

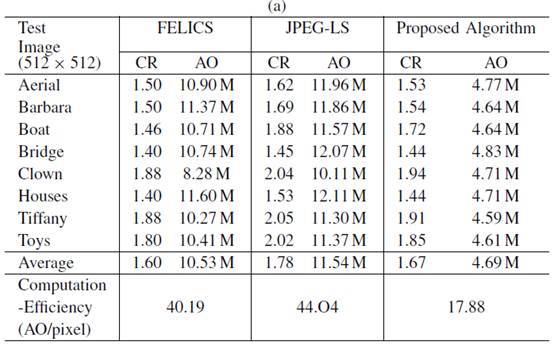

Performance Evluation:

[A] Lossledd coding

efficiency

[2] Arithmetic-operation Profiling